4-Gbit光纤通道数字时钟晶振设计的挑战

来源:http://www.taiheth.com 作者:泰河电子 2019年01月17

4-Gbit光纤通道数字时钟晶振设计的挑战

低抖动晶振传输信号考虑因素适用于任何高速和高频时钟分配系统,高频晶振电子产品要低定时抖动,不仅抖动特性差影响数据错误,但也可能导致失败使用信号源作为参考的锁相环,因此,当设计师接近项目时将一个高速数字应用于程序,他们需要考虑各种信号完整性低速时不需要的规定应用程序,规划高速数字化的关键挑战项目包括大限度地减少定时抖动,本文要提到的是高速数字时钟设计的挑战生成和分配工作.

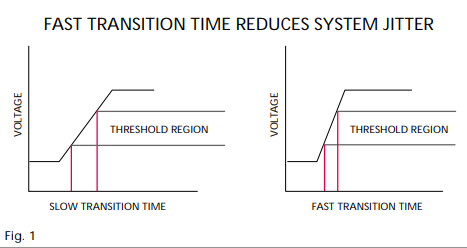

在更高的速度,传输线和他们的组件表现不同他们以较低的速度做,产生这样的信号完整性问题,如抖动,噪声,反射和如果没有正确指定和配置串扰,如果源要用作显示时钟参考,结果将是模糊的显示,通常,时钟晶振信号通过的速度越快过渡区域,系统抖动越小生产(见图1),减少排放,在高速应用中,产生电磁干扰的可能性(EMI)急剧增加,FCC规定关于EMI降噪正在变得越来越多更快的数字速度更严格. 设计师需要解决传输等特性线,差分信号,信号幅度和谐波含量以最大化能量将被送到负载,从而减少能量排放量,确保稳定,一般来说,越高规定的电子工作频率你正在设计的系统,越关键时钟稳定性是,时钟性能不稳定会导致误码率增加,错误无论是数据系统中的数据还是错过的数据它们是本地或广域系统,传输线阻抗匹配,该整个传输的阻抗和长度必须测量线并与每个线匹配终止,如果忽略阻抗匹配,可能发生发射,串扰和反射.

实现最佳系统性能的关键在高速应用程序开始有效时钟生成和分配的设计方法,简而言之,设计师应该采用一个解决各种时钟生成的方法和分配组件一样完整解决方案,而不是单个部分,小心关注选择适当的组件和电路分配方法应在项目的开始,牢记相互关系组件彼此之间,进一步,考虑特征阻抗很重要的所有有源晶振和无源晶振元件随着设计的进展,操作频率.

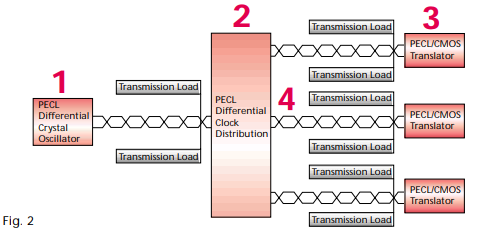

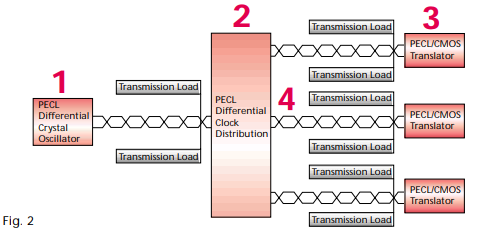

电源考虑因素,首要考虑因素这是为了确保时钟无噪音,低电源消耗今天的要求也在增加更高速的系统,正确选择以下时钟生成和分配组件是必不可少的(见图2):1.石英晶体振荡器及其输出逻辑2.时钟驱动程序,在某些情况下会包含启用功能3.5V或3V电源的CMOS转换器传输线(双绞线,同轴电缆,PCB走线)本白皮书旨在帮助您制作有关这些时钟生成的明智决定接近你的时候和分配组件下一个高速数字系统设计.

石英晶体振荡器和逻辑选择选择合适的晶体振荡器是在高速应用中至关重要,因为它将提供时钟参考全时钟分配系统,通常是严格的晶体振荡器应用要求频率稳定性为±20ppm,快速上升并且下降时间小于600皮秒,低特征抖动和正耦合发射极逻辑PECL差分输出,频率稳定性将提供可靠的系统参考,而波形的快速上升和下降时间将会导致系统抖动低,(虽然饱和了可以引入快速上升和下降时间的过渡不需要的噪音,这种噪音将被取消使用差分信号.)

石英晶体振荡器和逻辑选择选择合适的晶体振荡器是在高速应用中至关重要,因为它将提供时钟参考全时钟分配系统,通常是严格的晶体振荡器应用要求频率稳定性为±20ppm,快速上升并且下降时间小于600皮秒,低特征抖动和正耦合发射极逻辑PECL差分输出,频率稳定性将提供可靠的系统参考,而波形的快速上升和下降时间将会导致系统抖动低,(虽然饱和了可以引入快速上升和下降时间的过渡不需要的噪音,这种噪音将被取消使用差分信号.)

晶体振荡器质量除了确保波形中的低抖动外,设计人员应确保抖动最小化在振荡器本身,这是通过选择来实现的包含非常高Q值振荡器,此外,晶体应调整到振荡器电路由振荡器优化制造商,因为振荡器特性随负载阻抗而变化和负载偏置电压,重要的是指定正在使用的实际负载和通信设备,这对晶振供应商来说时钟驱动的另一个方面应该是结构性设备的对称性,这反映在整体信号稳定性更好.

低抖动晶振传输信号考虑因素适用于任何高速和高频时钟分配系统,高频晶振电子产品要低定时抖动,不仅抖动特性差影响数据错误,但也可能导致失败使用信号源作为参考的锁相环,因此,当设计师接近项目时将一个高速数字应用于程序,他们需要考虑各种信号完整性低速时不需要的规定应用程序,规划高速数字化的关键挑战项目包括大限度地减少定时抖动,本文要提到的是高速数字时钟设计的挑战生成和分配工作.

在更高的速度,传输线和他们的组件表现不同他们以较低的速度做,产生这样的信号完整性问题,如抖动,噪声,反射和如果没有正确指定和配置串扰,如果源要用作显示时钟参考,结果将是模糊的显示,通常,时钟晶振信号通过的速度越快过渡区域,系统抖动越小生产(见图1),减少排放,在高速应用中,产生电磁干扰的可能性(EMI)急剧增加,FCC规定关于EMI降噪正在变得越来越多更快的数字速度更严格. 设计师需要解决传输等特性线,差分信号,信号幅度和谐波含量以最大化能量将被送到负载,从而减少能量排放量,确保稳定,一般来说,越高规定的电子工作频率你正在设计的系统,越关键时钟稳定性是,时钟性能不稳定会导致误码率增加,错误无论是数据系统中的数据还是错过的数据它们是本地或广域系统,传输线阻抗匹配,该整个传输的阻抗和长度必须测量线并与每个线匹配终止,如果忽略阻抗匹配,可能发生发射,串扰和反射.

实现最佳系统性能的关键在高速应用程序开始有效时钟生成和分配的设计方法,简而言之,设计师应该采用一个解决各种时钟生成的方法和分配组件一样完整解决方案,而不是单个部分,小心关注选择适当的组件和电路分配方法应在项目的开始,牢记相互关系组件彼此之间,进一步,考虑特征阻抗很重要的所有有源晶振和无源晶振元件随着设计的进展,操作频率.

电源考虑因素,首要考虑因素这是为了确保时钟无噪音,低电源消耗今天的要求也在增加更高速的系统,正确选择以下时钟生成和分配组件是必不可少的(见图2):1.石英晶体振荡器及其输出逻辑2.时钟驱动程序,在某些情况下会包含启用功能3.5V或3V电源的CMOS转换器传输线(双绞线,同轴电缆,PCB走线)本白皮书旨在帮助您制作有关这些时钟生成的明智决定接近你的时候和分配组件下一个高速数字系统设计.

晶体振荡器质量除了确保波形中的低抖动外,设计人员应确保抖动最小化在振荡器本身,这是通过选择来实现的包含非常高Q值振荡器,此外,晶体应调整到振荡器电路由振荡器优化制造商,因为振荡器特性随负载阻抗而变化和负载偏置电压,重要的是指定正在使用的实际负载和通信设备,这对晶振供应商来说时钟驱动的另一个方面应该是结构性设备的对称性,这反映在整体信号稳定性更好.

正在载入评论数据...

相关资讯

- [2023-07-12]康纳温菲尔德推出符合Stratum3E...

- [2023-06-26]选择石英晶体要了解的必要参数,...

- [2023-06-25]艾伯康公司发布连续电压有源晶振...

- [2021-01-18]今日主题:什么样性能的石英晶振...

- [2021-01-13]是什么原因造成晶振相噪恶化?都...

- [2020-12-09]干货干货!爱普生旗下SG-8018系列...

- [2020-09-08]石英Crystal工作原理是怎样的,这...

- [2020-09-01]Oscillator的制造流程究竟是怎样...